6月10日、IntelはLakefieldことIntel Core Processors with Intel Hybrid Technology2製品を発表したが、これに先立ち6月はじめに、Comet LakeのDatasheet(正式名称は"10th Generation Intel Core Processor Datasheet")を公開した。正確に言えば、このドキュメントのVolume 2は5月に公開されているが、Volume 1が6月まで公開されなかった(*1)。このVolume 1でComet LakeのPL2の値が判明したので、まずはこれをご紹介したいと思う。

Comet LakeのPL1とPL2

さて、そもそもPL1/PL2/PL3/PL4とは何か? という話から。Photo01はそのDatasheetからの抜粋であるが、ちょっと見難い黄色(というか黄土色)がProcessorの消費電力変動である。PL1(Power Limit 1)が、いわゆるTDPとして理解されている消費電力枠であり、通常はこれを超えない様に調整される。

ただし、熱的にゆとりがある(Tcase:ケース温度とTjunction:トランジスタのジャンクション温度がどちらも上限より低い事が必須)場合、一時的にこれを超えて消費電力を引き上げる事が可能である。これがPL2(Power Limit 2)で、ここにあるように概ね100秒程度のタイマー付きである。勿論タイマーの限界までPL2で駆動出来る訳ではなく、この途中で熱的に上限に達したらPL1に強制的に推移することになる。ただこの強制推移までの時間は、当然ながらどんな冷却機構を使っているかで変わってくるが。

PL3とPL4は、一時的にPL2を超えて消費電力を増やすことを許す仕組みであるが、ただし最大でも10ms以下ということで、絶対的な消費電力としてはそれほど大きくはない。ただこのPL3/PL4が有効になった場合、VRMは当然これに追従しないといけないので、更に設計が難しくなりそうだ。ただ現状Coffee LakeやComet LakeでPL3/PL4が有効になっている製品は無く、なのでPL1とPL2のみを考慮すればよい。

ちなみにPL2の最大許容時間を定めているのがPL1 Tauというパラメータである。これは通常秒単位で設定される。

ということで、まずはCoffee Lake世代の第9世代Coreプロセッサはどんな感じになっているのか、が表1である。PL1はTDPそのままであり、PL2はその25%増で一律になっている。またPL1 TauのRecommendedは28秒(Maxは448秒)になっており、あとはBIOS Settingの奥深いところでこのあたりのパラメータをいじらなければ、基本的には30秒弱でPL2は終了し、あとはPL1で動作することになる。

| ■表1 | |||||

| Core Count | TDP | Processor Number | PL1(W) | PL2(W) | PL1 Tau(sec) |

|---|---|---|---|---|---|

| 8core | 127W | i9-9900KS | 127 | 127*1.25 | 28 |

| 95W | i9-9900K i7-9700K |

95 | 95*1.25 | 28 | |

| 65W | i9-9900 i7-9700 |

65 | 65*1.25 | 28 | |

| 35W | i9-9900T i7-9700T |

35 | 35*1.25 | 28 | |

| 6core | 95W | i5-9600K | 95 | 95*1.25 | 28 |

| 65W | i5-9600 i5-9500 i5-9400 |

65 | 65*1.25 | 28 | |

| 35W | i5-9600T i5-9500T i5-9400T |

35 | 35*1.25 | 28 | |

| 4core | 91W | i3-9350K | 91 | 91*1.25 | 28 |

| 65W | i3-9100 | 65 | 65*1.25 | 28 | |

| 62W | i3-9320 i3-9300 |

62 | 62*1.25 | 28 | |

| 35W | i3-9300T i3-9100T |

35 | 35*1.25 | 28 | |

ではComet Lakeこと第10世代Coreプロセッサは? というのが表2である。まず倍率変更可能なKシリーズはPL1 Tauが倍の56秒になっており(最大値は同じく448秒)、しかも最大250Wである。ちょっと目を疑ったが、要するに倍だ。もっとも倍率だけで言えば、TDP 35Wの筈のCore i9-10900TなどPL2が123Wで、PL1の3.5倍もの消費電力を許容する。TDP 125Wの製品はそれなりに消費電力が大きい事をユーザーが理解しているからいいが、TDP 65Wの製品ですら、なんと200Wを超えるPL2が設定されている。Comet Lakeの性能アップは、このPL2の設定がその根源にある事が良くわかる。

| ■表2 | |||||

| Core Count | TDP | Processor Number | PL1(W) | PL2(W) | PL1 Tau(sec) |

|---|---|---|---|---|---|

| 10core | 125W | i9-10900K | 125 | 250 | 56 |

| 65W | i9-10900 | 65 | 224 | 28 | |

| 35W | i9-10900T | 35 | 123 | 28 | |

| 8core | 125W | i7-10700K | 125 | 229 | 56 |

| 65W | i7-10700 | 65 | 224 | 28 | |

| 35W | i7-10700T | 35 | 92 | 28 | |

| 6core | 125W | i5-10600K | 125 | 182 | 56 |

| 65W | i5-10600 i5-10500 i5-10400 |

65 | 134 | 28 | |

| 35W | i5-10600T i5-10500T i5-10400T |

35 | 92 | 28 | |

| 4core | 65W | i3-10320 i3-10300 i3-10100 |

65 | 90 | 28 |

| 35W | i3-10300T i3-10100T |

35 | 55 | 28 | |

以前のComet Lakeのベンチマーク記事の中で、TMPGEnc Video Mastering Works 7の消費電力変動のグラフが判りやすいかと思うが、Core i7-10700Kが一番PL1/PL2モデルに近い動きをしている。最初の60秒位までは224.8Wほど消費電力が増加しており、その後は141.8Wに落ちている。Core i9-10900Kはコア数が多い分、少し早めに温度が上がりすぎてしまったためか、40秒ほどでPL1に戻っているが、そこまでの間は平均で230Wちょいまで消費電力が増えており、ほぼPL2のLimitに当たっている感じである。なるほど、Coffee LakeのCore i9-9900Kと全く傾向が異なる訳である。

Comet LakeでPL1 Tauを56秒に増やした理由であるが、ベンチマーク対策が無かったとは言えない。例えばCineBench R20、All CPUの場合はスタートから終了まで1分かからない。ここでPL1 Tauが28秒だと、ベンチマークが完了する前にPL1に落ちてしまうが、56秒ならPL2のまま完走する。あるいは3DMarkのPhysicsやCPU Benchも同じで、大体1分程度だから、PL1 Tauが56秒あれば全部は無理にしても大半をカバーできることになる。

ご存じの様に今年はCOMPUTEXが中止になってしまった。その代わりに、Onlineの形でキーパーソンによるメッセージが公開されたが、IntelのBob Swan CEOは自身のメッセージの中で、"We should see this moment as an opportunity to shift our approach from the benchmark industry to the benefits and impacts of the technology we create"(Photo02)と述べている。「そろそろベンチマークの性能で判断するのではなく、性能がもたらすベネフィットで判断すべきだ」という事だそうだが、Comet LakeのPL1がこのメッセージに反するものでなければよいのだが。

余談であるが、この250WものPL2を支えるため、IccMAX(プロセッサコアへの最大供給電流)は250Aに達している。なるほどLGA1200のマザーボードがいずれもゴツイVRMを搭載する筈であり、LGA1150のままでは供給電流が足りないから、Socketを変更しないと問題が起きても不思議ではない(Coffee Lake世代のIccMAXは193A)。50Aも流す電流が増えるとなれば、それはLandを増やしてVccとGNDを強化したくなる訳で、LGA1200に変更するのも無理ないところである。

(*1) 実は他にSpecification Updateも6月に公開されている筈なのだが、現時点ではアクセス不能である。

Lakefieldのスペックで未だ不可解な部分

2018年のIntel Architecture Dayで初めてその名前が出てきたLakefield。ただこの時は10nmで製造されたCoreと14nmで製造されたAtom+I/OをFoverosで立体化するという話で、まだコンセプトモデルに近いレベルの話であった。ただある意味これは目くらましであって、2019年のCESではかなり現実に近いモデルに切り替わった。その後、Sunny Coveの詳細やTremontの詳細も明らかにされた訳であるが、既に2製品がark.intel.comに登録されており、プレスリリースよりも詳細なスペックが公開されている。

表3はこれをまとめたものであるが、実は搭載メモリは4GBと8GBの2種類のSKUがあること、及び価格はCore i3/i5、4GB/8GBを問わず一律$281.00なことなどは普通にスペックを見ただけでは判らない仕組みになっている(価格は現時点では見られなくなっているので注意)。

| ■表3 | ||||

| Processor Number | i5-L16G7 | i3-L13G4 | ||

|---|---|---|---|---|

| CPU | コア/スレッド数 | 5/5 | ||

| キャッシュ容量 | 4MB | |||

| 動作周波数(GHz) | 定格 | 1.4 | 0.8 | |

| 1コア最大 | 3.0 | 2.8 | ||

| 全コア最大 | 1.8 | 1.3 | ||

| Memory | 種別 | LPDDR4X-4267 | ||

| 容量 | 4/8GB | |||

| バス幅 | 64bit | |||

| Graphics | EU数 | 64 | 48 | |

| 動作周波数(GHz) | 定格 | 0.2 | ||

| 最大 | 0.5 | |||

| TDP | 7W | |||

| 推奨小売価格 | $281.00 | |||

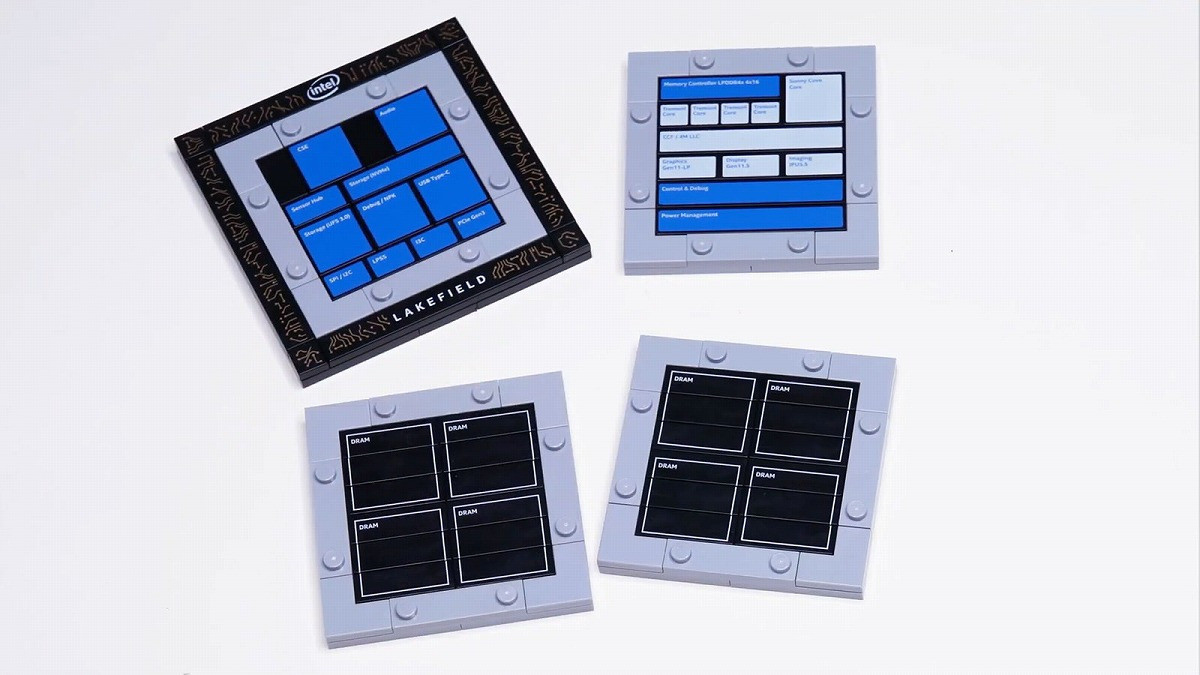

それはともかくとして、まずメモリについて。IntelはLakefieldの発表に合わせ、LEGOでLakefieldを作るという動画を公開しているが、これを見るとまずI/O Die(Photo03)、次いでProcessor Die(Photo04)と来て、次にDRAMが4つ搭載された層を「2つ」作り(Photo05)、しかもこれを積層している(Photo06)。という事はLPDDR4を最大8つ搭載できる? という事になるのだが、これは辻褄が合わない。昨年のInvestor Meetingの際のスライドでもDRAMは4つしかないからだ。また、LPDDR4xのI/FはPhoto04にもあるように、4×16bit構成である。現在のDRAMトップベンダー3社(Samsung、SK Hynix、Micron)はLPDDR4xに関しては16bit幅が一番小さい構成であり、8bit幅の製品はリリースしていない。となると、メモリを2層積層してもそれを利用する方法がない。

可能性としては

- スペシャルでx8構成のLPDDR4xを作ってもらい、2段積層の場合はこれを利用する

- 実はMemory I/Fは4×32で、ただし最初のリリースはこのうち4×16しか使わない

- 将来は2段積みを考慮するが、現状は未対応

- ただのジョーク

あたりで、3番目か4番目の公算が非常に高い気がするのだが。とにかくMemoryに関してはそんな訳でちょっと不可解である。ただとりあえず今回発表された2製品に関しては、LPDDR4xが4つという構成は間違いない様だ。

次がCPUコアにまつわる話。表3にもある様に、例えばi5-L16G7なら全コア最大が1.8GHz、1コア最大が3GHzとなっているが、おそらくTremontコアはこの1.8GHzが最大で、これを超えられるのはSunny Coveコアだけという設定になっていると思われる。まぁそれはいいとして、面白いのはこれが5コア5スレッド構成になっている事だ。つまりSunny CoveとTremontはどちらもHyper-Threadingが利用可能にもかかわらず、これを無効化していることになる。

もう一つ面白いのが拡張命令。TremontはSSE 4.2までのサポートであるが、その代わりに新しくCrypto accelerationとかGFNI(Galois Field New Instructions)が追加された、という話はこちらで紹介した通りだ。一方で、Sunny CoveはGFNIこそないもののAVX512までのサポートがある。ではLakefieldは? というと、この両者の最大公約数を取った形になった。つまり拡張命令はSSE 4.2までで、AVXもGFNIも無しである。

なんでこんなことになったか? 筆者が考えるに、これはWindows 10のスケジューラ絡みの問題である。やはりここで書いた通り、MicrosoftはSnapdragonベースのArm SoCにWindows 10 on Armを載せる過程で、Armのbig.LITTLE/DynamIQをスケジューラでサポートしている。そしておそらくこのスケジューラをそのままLakefieldに応用するのではないかと予想したが、これが予想通りだったという事だ。というのはbig.LITTLE/DynamIQは

- 最大でも8コアまで、世の中にはこれを超えて10コア搭載のSoCもある(古い所ではMediatekのHelio X30)が、これに関してはそのベンダーが独自のスケジューラを提供する(MediaTekの場合はCorePilotと呼ばれる独自スケジューラが用意される)ことで解決しており、一般的ではない。Qualcommはこの点に関してはArmのガイドラインに従い、最大8コアまでの製品しか出しておらず、Windows 10 on Armの実装も当然これに則ったものになる。

- 同一命令セットが必要 big.LITTLEにせよDynamIQにせよ、サポートする命令セットは完全に同一である必要がある。つまり命令によるスケジューラのDispatchは行われない。

という2つの制限がある。今回、Hyper-Threadingを無効化したのも、これを有効化すると10コア相当になってしまい、8コア制限を超えてしまう事になる。また対応命令セットを最小公約数的に設定したのも、これが理由に思える。

逆に言えば、これはWindows 10ベースでMicorosftの提供するスケジューラを使う限り避けえない話になる訳だが、それ以外の、例えばLinux向けのスケジューラを自身で手を入れれば、このあたりの制限が回避される可能性がある。もっとも、そうしたニーズがどこまであるのか、という話ではあるのだが。これは次のバリエーションの話に繋がる。

そのバリエーションの話。今回はTDP 7Wの製品が2つ発表されただけだが、少なくともTDP(というか、PL1)が5Wの製品が予定されていたことはこちら(Photo08)からも明らかである。ちなみに現在のLakefieldのPL2がどの程度かは現状未公開(9.5W、という数字が流れてきているが、確定情報ではない)である。

で、これで終わりか? というと良くわからないのだが、可能性的にはより消費電力を引き上げた製品があっても良さそうに思える。現状の7WというのはY SKUに相当する訳だが、U SKUは狙っても問題ない気がする。PL1が15W、PL2が25~27Wというカテゴリーだ。なんでそう思うかと言えば、ハードウェアを変えないままでも例えば

- Sunny CoveのHTを有効にして、2+4コア構成

- TremontのHTを有効にし、ただしコアを半分無効化して1+4コア構成

にすれば、前者は7Wの枠ははみ出すにしてももう少し性能が上がるし、後者は性能こそ落ちるが消費電力は更に落ちるだろう。Pentium/CeleronグレードのLakefieldが必要になった場合には後者の構成が役に立つはずだ。

またLakefieldでは現状、異様にGPUの動作周波数が低い。定格200MHz、Turboでも500MHzというのは、ダイサイズを考えるとかなり無駄が多い。実際この周波数なら、EU数を半減させ、動作周波数を倍にしても恐らく消費電力は変わらない筈だ。ただ、仮にTDP 15W枠になって動作周波数を引き上げるとなると、話が変わる。15W枠なら700~800MHz程度まで動作周波数は引き上げられるだろう。この範囲だと、まだ消費電力が急増はしないからだ。ただこれを倍速(1.4~1.6GHz)で動かすとなると、消費電力がグンと跳ね上がると思われる。多分Lakefieldの64EU構成は、1GHzを超えない範囲で使う事を前提にデザインされたのだろう、と想像される。現在はこれをY SKU相当の7Wで動かしているから妙に動作周波数が低いが、本来はU SKU相当の製品を念頭に考えたのではないかと筆者は予測している。

もっともそうした製品が本当に世に出るかどうかは未知数である。とにかくスケジューラ周りが厄介というのが実情であり、はたしてSurface Neoに続く製品がどこまで出てくるか。その意味ではどこまでSurface Neoが売れるか次第で決まるのかもしれない。

"わかった" - Google ニュース

June 17, 2020 at 07:18AM

https://ift.tt/3e49ipw

「Comet Lake」と「Lakefield」について新しく深くわかった事 - マイナビニュース

"わかった" - Google ニュース

https://ift.tt/2UITuSs

Shoes Man Tutorial

Pos News Update

Meme Update

Korean Entertainment News

Japan News Update

No comments:

Post a Comment